Best paper for a low-power ADC circuit for brain-machine interface applications

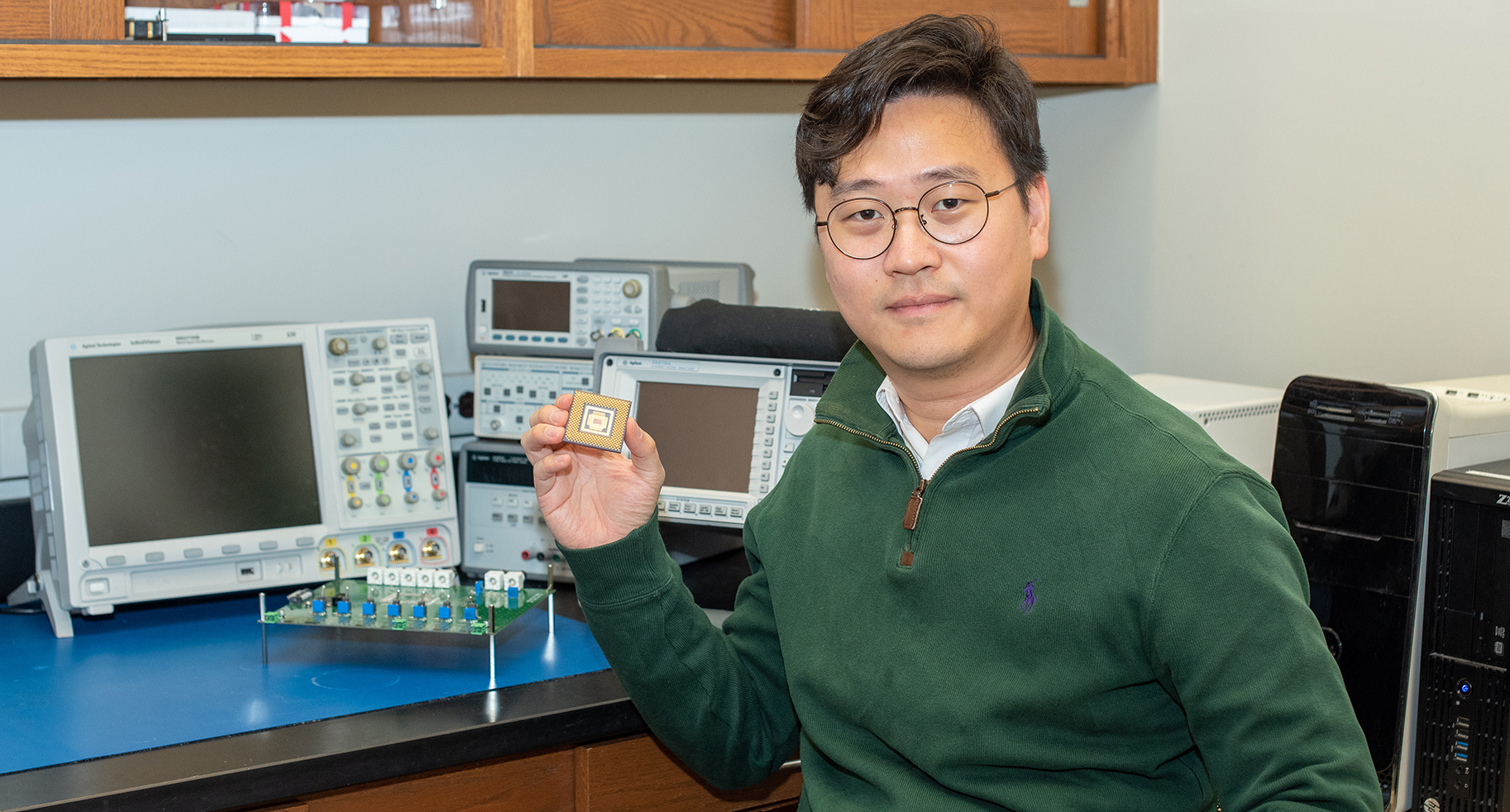

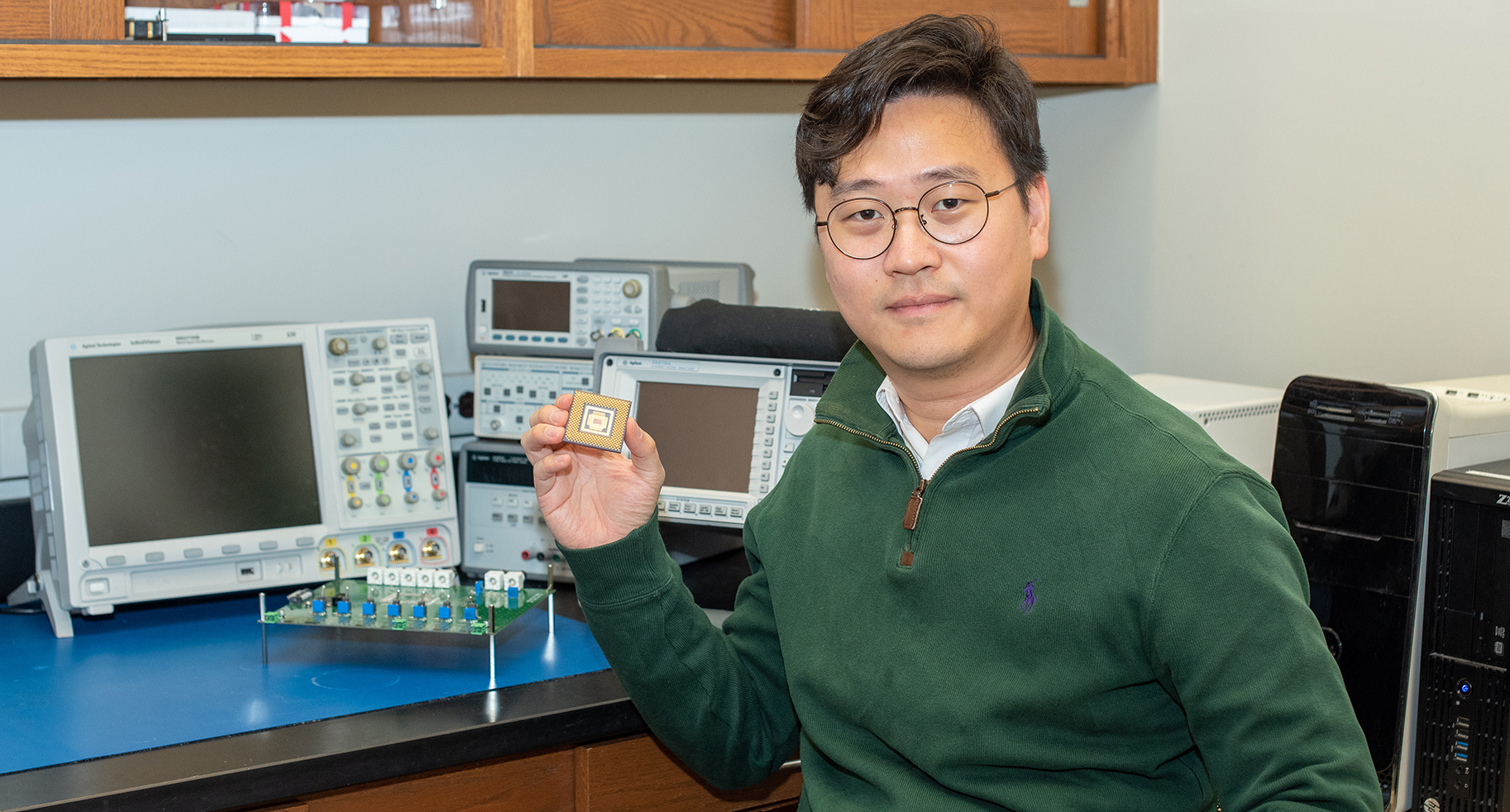

Euisik Yoon’s team, led by Sungjin Oh, developed a low-power neural recording front-end circuit to interface with state-of-the-art neural probes.

Euisik Yoon’s team, led by Sungjin Oh, developed a low-power neural recording front-end circuit to interface with state-of-the-art neural probes.

Research improving the neural recording process in a brain-machine interface received a Best Paper Award at the IEEE Biomedical Circuits and Systems Conference (BIOCAS 2022), held in Taiwan. Specifically, the team developed a low-power neural recording front-end circuit designed for an implantable high-channel count brain interface system.

“With surging interest in brain-machine or brain-computer interfaces,” said first author and doctoral student Sungjin Oh, “this work can improve their performance, and eventually make them more useful for scientific research or clinical purposes.”

Analysis of the complex neuronal network in the brain requires the sophisticated acquisition process of subcortical neural signals in multiple sites. Analog mixed-signal neural recording front-end circuits are able to conduct this important role of acquiring and conditioning brain signals in microvolt-scale. However, optimizing their power-noise performance is critical to achieving a high-quality and high-density neural interface.

An essential piece to implementing such an interface system, explained Oh, is a low-power neural recording front-end circuit that can operate with a small battery.

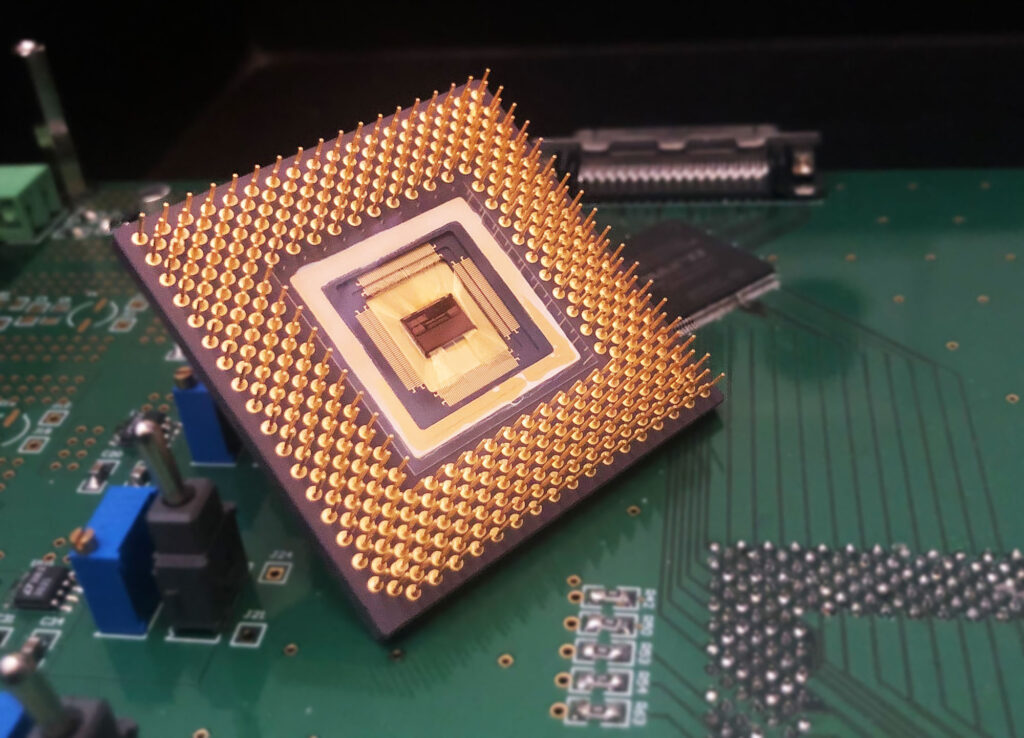

Such circuits require an analog-to-digital converter (ADC) to translate the brain signals into information that can be interpreted by a computer, but ADCs tend to be power hungry. This is especially true for incremental ADCs (IADCs), which are particularly well suited for the target application. Lowering the power consumption of the IADC makes it possible to be implanted along with neural probes, thereby providing much more information to scientists about the workings of the brain.

According to Oh, the power consumption of the IADC was dramatically reduced by exploiting the spectral characteristics of subcortical neural signal components in order to achieve an optimized energy-efficient signal acquisition system.

Through the novel technique of tracking and zooming into the neural signal dynamically, all the mixed components of neuronal activities were captured in low power analog-to-digital conversion with dual-band outputs.

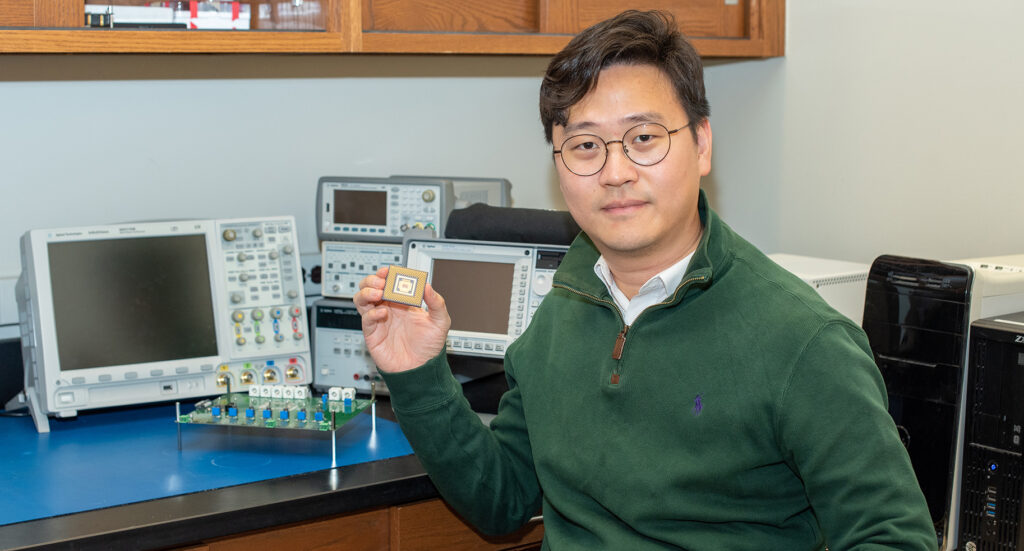

The fabricated dual-band neural recording front-end chip was connected to a multi-channel neural probe and tested in an in vivo experiment using a mouse. The probe was developed under the NSF Multimodal Integrated Neural Technologies (MINT) program.

The team reported that the chip successfully recorded the broadband neural signals, while also accurately tracking the local field potential (LFP) signal. At the same time, the scheme reduced the analog power consumption of the 2nd order IADC by 64.3%.

According to Oh, in addition to improving the design of the neural recording front-end circuit, the team improved the overall interface system efficiency in terms of digital post-processing resources.

The research was described in the paper, “LFP-Adaptive Dynamic Zoom-and-Tracking Dual-Band Neural Recording Front-End Using a Power-Efficient Incremental Delta-Sigma ADC,” by doctoral student Sungjin Oh, who presented the research, Hyunsoo Song, Nathan Slager, Jose Roberto Lopez Ruiz, alumnus Sung-Yun Park, and research supervisor and professor Euisik Yoon.